详细讲解MOSFET管驱动电路

在使用MOS管设计开关电源或者马达驱动电路的时候,大部分人都会考虑MOS的导通电阻,最大电压等,最大电流等,也有很多人仅仅考虑这些因素。这样的电路也许是可以工作的,但并不是优秀的,作为正式的产品设计也是不允许的。

下面是我对MOSFET及MOSFET驱动电路基础的一点总结,其中参考了一些资料,非全部原创。包括MOS管的介绍,特性,驱动以及应用电路。

1,MOS管种类和结构

MOSFET管是FET的一种(另一种是JFET),可以被制造成增强型或耗尽型,P沟道或N沟道共4种类型,但实际应用的只有增强型的N沟道MOS管和增强型的P沟道MOS管,所以通常提到NMOS,或者PMOS指的就是这两种。

至于为什么不使用耗尽型的MOS管,不建议刨根问底。

对于这两种增强型MOS管,比较常用的是NMOS。原因是导通电阻小,且容易制造。所以开关电源和马达驱动的应用中,一般都用NMOS。下面的介绍中,也多以NMOS为主。

MOS管的三个管脚之间有寄生电容存在,这不是我们需要的,而是由于制造工艺限制产生的。寄生电容的存在使得在设计或选择驱动电路的时候要麻烦一些,但没有办法避免,后边再详细介绍。

在MOS管原理图上可以看到,漏极和源极之间有一个寄生二极管。这个叫体二极管,在驱动感性负载(如马达),这个二极管很重要。顺便说一句,体二极管只在单个的MOS管中存在,在集成电路芯片内部通常是没有的。

2,MOS管导通特性

导通的意思是作为开关,相当于开关闭合。

NMOS的特性,Vgs大于一定的值就会导通,适合用于源极接地时的情况(低端驱动),只要栅极电压达到4V或10V就可以了。

PMOS的特性,Vgs小于一定的值就会导通,适合用于源极接VCC时的情况(高端驱动)。但是,虽然PMOS可以很方便地用作高端驱动,但由于导通电阻大,价格贵,替换种类少等原因,在高端驱动中,通常还是使用NMOS。

3,MOS开关管损失

不管是NMOS还是PMOS,导通后都有导通电阻存在,这样电流就会在这个电阻上消耗能量,这部分消耗的能量叫做导通损耗。选择导通电阻小的MOS管会减小导通损耗。现在的小功率MOS管导通电阻一般在几十毫欧左右,几毫欧的也有。

MOS在导通和截止的时候,一定不是在瞬间完成的。MOS两端的电压有一个下降的过程,流过的电流有一个上升的过程,在这段时间内,MOS管的损失是电压和电流的乘积,叫做开关损失。通常开关损失比导通损失大得多,而且开关频率越快,损失也越大。

导通瞬间电压和电流的乘积很大,造成的损失也就很大。缩短开关时间,可以减小每次导通时的损失;降低开关频率,可以减小单位时间内的开关次数。这两种办法都可以减小开关损失。

4,MOS管驱动

跟双极性晶体管相比,一般认为使MOS管导通不需要电流,只要GS电压高于一定的值,就可以了。这个很容易做到,但是,我们还需要速度。

在MOS管的结构中可以看到,在GS,GD之间存在寄生电容,而MOS管的驱动,实际上就是对电容的充放电。对电容的充电需要一个电流,因为对电容充电瞬间可以把电容看成短路,所以瞬间电流会比较大。选择/设计MOS管驱动时第一要注意的是可提供瞬间短路电流的大小。

第二注意的是,普遍用于高端驱动的NMOS,导通时需要是栅极电压大于源极电压。而高端驱动的MOS管导通时源极电压与漏极电压(VCC)相同,所以这时栅极电压要比VCC大4V或10V。如果在同一个系统里,要得到比VCC大的电压,就要专门的升压电路了。很多马达驱动器都集成了电荷泵,要注意的是应该选择合适的外接电容,以得到足够的短路电流去驱动MOS管。

上边说的4V或10V是常用的MOS管的导通电压,设计时当然需要有一定的余量。而且电压越高,导通速度越快,导通电阻也越小。现在也有导通电压更小的MOS管用在不同的领域里,但在12V汽车电子系统里,一般4V导通就够用了。

MOS管的驱动电路及其损失,可以参考Microchip公司的AN799 Matching MOSFET Drivers to MOSFETs。讲述得很详细,所以不打算多写了。

5,MOS管应用电路

MOS管最显著的特性是开关特性好,所以被广泛应用在需要电子开关的电路中,常见的如开关电源和马达驱动,也有照明调光。

本文档由上海圣采自动化设备有限公司WWW.ISHENGCAI.COM整理提供

现在的MOS驱动,有几个特别的需求,

1,低压应用

当使用5V电源,这时候如果使用传统的图腾柱结构,由于三极管的be有0.7V左右的压降,导致实际最终加在gate上的电压只有4.3V。这时候,我们选用标称gate电压4.5V的MOS管就存在一定的风险。

同样的问题也发生在使用3V或者其他低压电源的场合。

2,宽电压应用

输入电压并不是一个固定值,它会随着时间或者其他因素而变动。这个变动导致PWM电路提供给MOS管的驱动电压是不稳定的。

为了让MOS管在高gate电压下安全,很多MOS管内置了稳压管强行限制gate电压的幅值。在这种情况下,当提供的驱动电压超过稳压管的电压,就会引起较大的静态功耗。

同时,如果简单的用电阻分压的原理降低gate电压,就会出现输入电压比较高的时候,MOS管工作良好,而输入电压降低的时候gate电压不足,引起导通不够彻底,从而增加功耗。

3,双电压应用

在一些控制电路中,逻辑部分使用典型的5V或者3.3V数字电压,而功率部分使用12V甚至更高的电压。两个电压采用共地方式连接。

这就提出一个要求,需要使用一个电路,让低压侧能够有效的控制高压侧的MOS管,同时高压侧的MOS管也同样会面对1和2中提到的问题。

在这三种情况下,图腾柱结构无法满足输出要求,而很多现成的MOS驱动IC,似乎也没有包含gate电压限制的结构。

于是我设计了一个相对通用的电路来满足这三种需求。

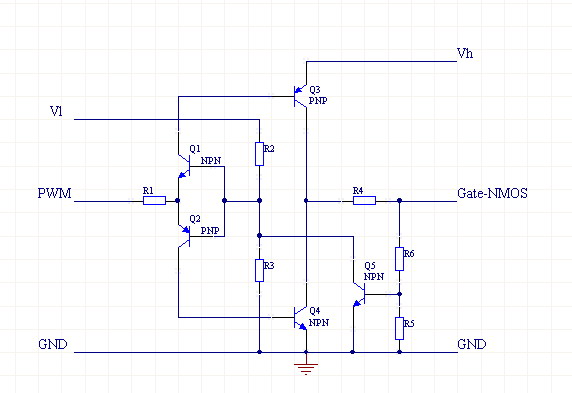

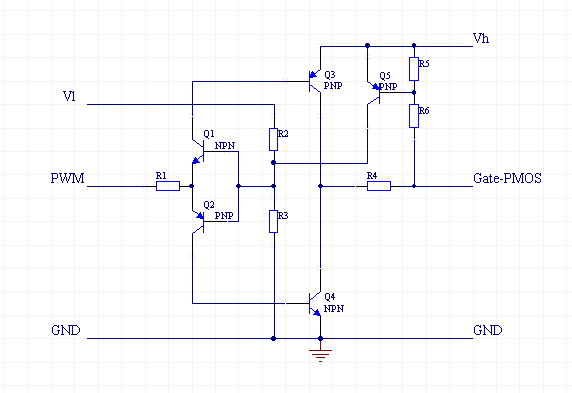

电路图如下:

图1 用于NMOS的驱动电路

图2 用于PMOS的驱动电路

这里我只针对NMOS驱动电路做一个简单分析:

Vl和Vh分别是低端和高端的电源,两个电压可以是相同的,但是Vl不应该超过Vh。

Q1和Q2组成了一个反置的图腾柱,用来实现隔离,同时确保两只驱动管Q3和Q4不会同时导通。

R2和R3提供了PWM电压基准,通过改变这个基准,可以让电路工作在PWM信号波形比较陡直的位置。

Q3和Q4用来提供驱动电流,由于导通的时候,Q3和Q4相对Vh和GND最低都只有一个Vce的压降,这个压降通常只有0.3V左右,大大低于0.7V的Vce。

R5和R6是反馈电阻,用于对gate电压进行采样,采样后的电压通过Q5对Q1和Q2的基极产生一个强烈的负反馈,从而把gate电压限制在一个有限的数值。这个数值可以通过R5和R6来调节。

最后,R1提供了对Q3和Q4的基极电流限制,R4提供了对MOS管的gate电流限制,也就是Q3和Q4的Ice的限制。必要的时候可以在R4上面并联加速电容。

这个电路提供了如下的特性:

1,用低端电压和PWM驱动高端MOS管。

2,用小幅度的PWM信号驱动高gate电压需求的MOS管。

3,gate电压的峰值限制

4,输入和输出的电流限制

5,通过使用合适的电阻,可以达到很低的功耗。

6,PWM信号反相。NMOS并不需要这个特性,可以通过前置一个反相器来解决。

- 上一篇:要成为plc编程高手的八大基础原则 [2014/11/20]

- 下一篇:变频电源系统工作原理 [2014/11/20]